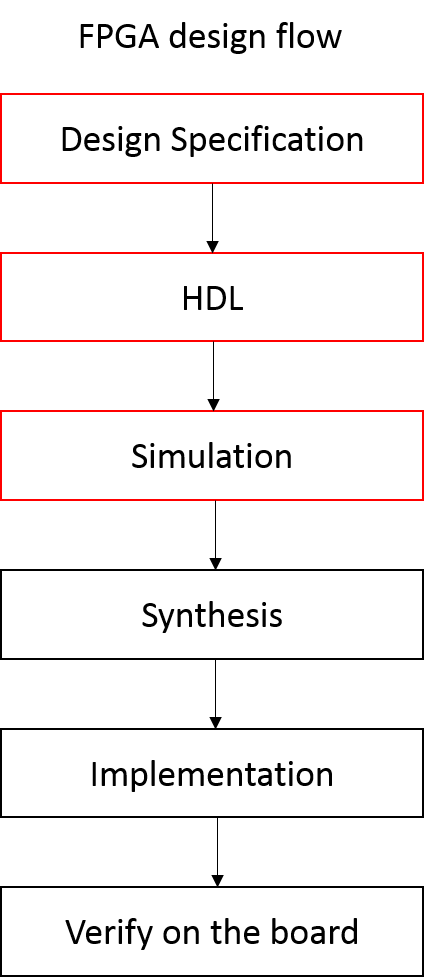

今天來聊一下FPGA 的 design flow,為什麼是FPGA而不是ASIC呢,因為這一系列的介紹都是用vivado這套工具去跑模擬,而這套工具就是為了Xilinx 所生產的FPGA而設計的,所以今天才會選擇FPGA design flow當為主題,首先先來看一下流程圖

之前介紹的電路應用,跑得波形圖都是在行為的正確性,並沒有考慮合成後的驗證,所以在flow底下,前面的系列只包含了前三個步驟,包括

Design Specification:決定要做什麼功能的電路,並規劃好架構,像是要用多少資源,速度要多快,FSM該怎麼切等等.

HDL:決定好架構之後就可以開始寫code了,可以是verilog或VHDL.

Simulation:寫完HDL之後緊接著就是寫testbench驗證行為正確性.

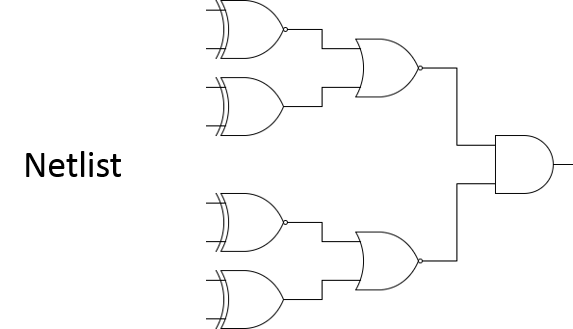

Synthesis:寫完的code需經過合成,把寫的HDL轉換成netlist 形式(gate-level),gate-level指的是把全部描述語言轉換成邏輯表示式,之後再做place&route時,就是以netlist為輸入檔,假設你寫一個之前提過的1-bit加法器,就會產生以下的netlist.v檔

module Full_Adder( A, B, Cin, Sum, Cout );

input A, B, Cin;

output Sum, Cout;

wire W1, W2, W3;

xor xor1( W1, A, B );

and and1( W2, W1, Cin );

and and2( W3, A, B );

xor xor2( Sum, W1, Cin );

or or1( Cout, W2, W3 );

endmodule

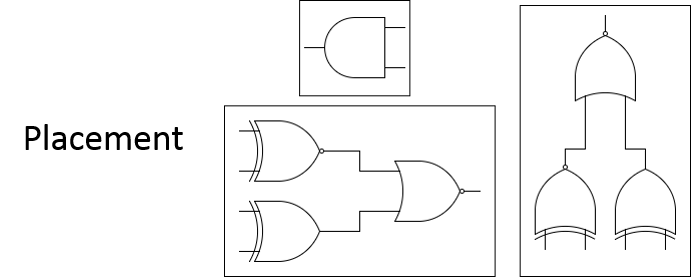

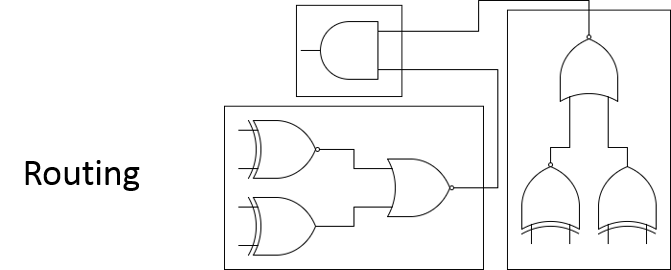

Implementation::當產生完netlist檔之後,就須決定各個module裡面邏輯閘的擺放位置以及繞線,這個步驟是非常重要的,因為這牽涉到電路是不是一個及格電路,怎樣才算及格呢,除了要求的功能要對以外,timing也要MET,意思是假設clock是100MHz,你的邏輯運算加上繞線的時間需要在10ns內完成,所以除了電路要寫的簡潔,在配合EDA tool的演算法最終才能完成一個及格的電路,至於如果遇到timing的問題我明天再跟大家分享,以下是一個簡單的implementation的流程圖供大家參考:

Verify:最後就是上板子實際驗證電路的正確性,一般來說,testbench驗證對了,timing也沒有問題的話,最後的電路大多都沒什麼問題,明天會再跟大家聊聊timing的問題.

請問MET是甚麼意思

MET是符合達到的意思,文中「timing也要MET」是指通常會設定一些時序上的限制,例如時脈的速度,而因為有設定目標,所以要確認有沒有達到條件